MEMORY SEGMENTATION

The memory in 8086 is organized as segmented memory. The total memory divided into a number of logical segments each spaced is 64k bytes in size and is addressed by one of the segment registers. To address a specific memory location within a segment, we need an offset address.

The CPU 8086 is able to address 1Mbyte of physical memory. This 1Mbyte is distributed as 64k bytes size to the 16 segments. Here we need to study the types of segments one is overlapping segments and another is non-overlapping segments.

The overlap segment arise when one segment start before 64kbytes of first segment. The non-overlap segment arises systematically by fill up the first segment and later another.

The main advantage of segmented memory scheme as follows:

1. Allow the memory capacity to the 1Mbytes and distributed each segment size of 64k bytes

2. For the protection of data and code, it allows the placing of memory of same program in different segment.

3. Provision for relocation may be done.

In 8086 based system, the 1Mbytes memory is organized as odd bank and even bank with two enables signals BHE and AO for selection of odd, even or both. From 1Mbyte each of 512k bytes addressed in parallel by the processor.

*Even address byte data transfer on D7-D0, while the byte data will odd address is transferred on D15-D8 bus line.

If a processor fetches a word from memory there are different possibilities like:

1. Both the bytes may be operands

2. Both the bytes may contain opcode bits

3. One of the bytes may be opcode while the other may be data.

The internal decoder of microprocessor takes care about the all possibilities. It also identifies the opcodes and operands which further derives the signals those act as input to the timing and control unit which help in execution of the instruction.

In referring word data, the BIU (Bus Interference Unit) requires one or two memory cycles the starting byte is located at an even or odd address.

*If word is located is even address, only one read or writes cycle is required. This even data is always better.

*If word is located in odd address, first read or write cycle is required for accessing the lower byte while the second one is required for accessing the upper byte. Thus two bus cycles are required.

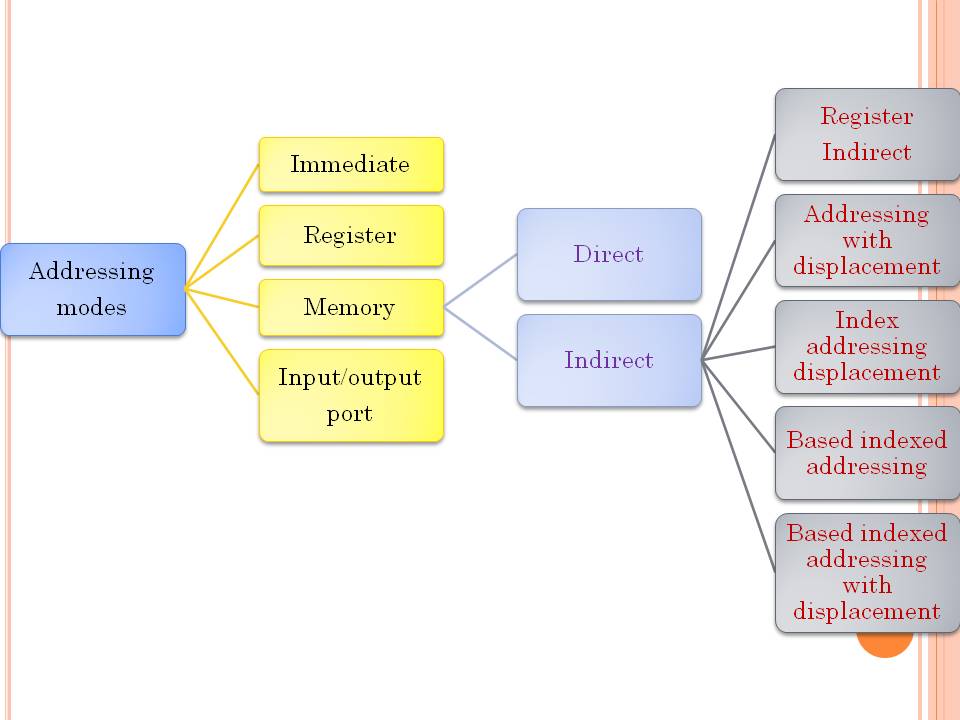

ADDRESSING MODES

Microprocessor provides the convenience of the programmer various method for accessing data needed in execution of an instruction. These various methods of accessing data are called the Addressing modes.

MEMORY ADDRESS MODES

The 8086 microprocessor generates 20 bit address to access the data in memory called physical address. This is done by adding 16 bit value called the Effective address. Effective address represents the offset of the desired operand from the starting address of the segment. Generally DS (Data segment) register is used as a segment register to generate the physical address, while accessing the data from memory.

In string instructions, the ES(Extra segment) register is used as segment register to generate the physical address of destination string.

Memory addressing is of two types

1. Direct memory addressing

2. Indirect memory addressing

1.Direct memory addressing:

In direct addressing mode 16 bit EA is provided in the instruction itself . The 20 bit physical address is generated using DS(Data segment) register in the direct addressing mode.

EX: MOV CL,KSR

The source operand is specified in direct addressing mode, KSR is a symbolic memory location, specified using DB assembler directive in the data segment. The location is specified by the instruction code given by EA which is 16 bit offset generated by assembler. The destination is specified by using register addressing.

Suppose the offset value corresponding to KSR is 2000H, the memory bytes location DS: 2000H is moved to CL

Before After

(DS: KSR) AB AB

(CL) 37 AB

2.Indirect addressing mode:

In indirect addressing mode, the 16 bit EA is not provided in the instruction itself. The physical address memory is 20bits. The source operand is not specified in Indirect addressing mode. In this mode the addressing is done by the other source on the influence of it.

The below video shows the clarification about the addressing modes:

The below video shows the clarification about the addressing modes:

The below video shows the clarification about the addressing modes Instruction set:

No comments:

Post a Comment